OSSによるLSI開発 OpenEDA と RISC-V (update)

2023年11月15日 OSS活用WG/技術本部本部長 竹岡尚三 (株)アックス

### 日本の半導体 産業 復興!

- ・国内8社が半導体製造会社「Rapidus」設立

- ・経産省キモ入り 「10年の遅れ」取り戻す

- ・キオクシア、ソニーグループ、ソフトバンク、 デンソー、トヨタ自動車、NEC、NTTが それぞれ10億円、三菱UFJ銀行が3億円を 出資した。

- ・ 半導体 工場は、かろうじて 最新のものがある

- ・でも、「お高いんでしょう~?」

- ・技術者 不足

- 半導体 設計 技術者

- 論理回路 設計 技術者

https://www3.nhk.or.jp/news/html/20221111/k10013887921000.html

# 中華チップ強し! (^^;

https://www.seeedstudio.com/LicheePi-Nano-ARM926EJS-SoC-Development-Board-16M-Flash-p-2892.html

Sipeed Longan Nano RISC-V GD32VF103CBT6開発ボード

https://www.seeedstudio.com/Sipeed-Longan-Nano-RISC-V-GD32VF103CBT6-Development-Board-p-4205.html

#### Allwinner D-1@1GHz搭 載

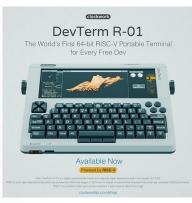

#### Clockworks DevTerm,uConsole

普通に**Linux,GUI**が使える https://www.clockworkpi.com/product-page/devterm-kit-r01

https://www.clockworkpi.com/product-page/devterm-kit-r01 https://www.clockworkpi.com/product-page/uconsole-kit-r-01 http://en.techinfodepot.shoutwiki.com/wiki/ClockworkPi\_Core\_R-01

#### LicheePi 4A

RISC-V@1.85GHz x4 50GFLOP GPU

https://wiki.sipeed.com/hardware/zh/lichee/th1520/lpi4a/1\_intro.html

#### M5Stamp C3U Mate ESP32-C3 RISC-V MCU ESP32のCPUがRISC-Vに

なった。//www.switch-science.com/catalog/7894/

#### M5Stack M5StickV

AIアクセラレータ付き RISC-V

https://www.switch-science.com/products/5700? fbclid=IwAR01nlN9ch9HkzyrCEg-eMPN\_qgfEw-1GaSgaS1iv5O0OW021h0dWdtekY0

### 技術者 不足をStop!日本の半導体 産業 復興!

- ・OSSの開発ツールで、LSI 開発

- ・ 無料ツールの使い手が増える → 技術者不足 解消!

- 半導体 設計 技術者

- 論理回路 設計 技術者

- ・ 半導体 工場は、「お高くない」ものもある

- レガシーファブ

- 65nm,90nm とか、安くて かなりいい

みんなのLSI 俺のASIC

### AISol の半導体事業の目標

国内の半導体アセット(チップ製造能力)を 本プロジェクトのプラットフォームに再整備することで 専用半導体の設計の参入障壁を下げ、

国内産業が専用半導体にて国際競争を勝ち抜く環境を提供 する。

Open Source Silicon for Japan

# Open-Source は、ロングテール 半導体開発の夢を見るか?

Do Open-Source Dream of Long-Tail

Semiconductors? –

11.17(金) 15:30-16:10 | 展示会場内 Room E

**AIST Solutions**

半導体事業 プロデューサー 岡村 淳一

### 半導体(LSI) 開発が OSSで自由な世界に

# Googleがカスタム半導体の民主化・自由化を推進

- ・Googleなどが、OSSを使用して、 LSI開発の民主化を行っている。2020年ごろより

- ・日本政府も、半導体産業 復興を行う

- •LSI開発者の裾野を広げる

- 零細企業でも、LSI設計ができる時代になった

- Open EDAを活用(Googleにならう)

- •OSSのハードウェア開発ツールを使用

- ・専用LSIは、低消費電力=持続可能社会に貢献

- ・汎用CPU, Intel x86は電力消費が大きすぎる

・我々は、OSSのハードウェア開発ツール 振興を行う!

# Googleがカスタム半導体の民主化・自由化を推進

- Googleと半導体ファウンドリの「SkyWater」が協力し、業界初となるオープンソースの PDKを公開

- Skywaterは2017年に米Cypress Semiconductorからスピンオフしたファウンドリ企業

- PDK プロセス設計キット

- ある特定の半導体プロセスで回路設計を行う際に必要な設計情報

- •トランジスタ配置の制約条件などが書かれている

- 半導体の設計者は、半導体製造のファウンドリから「Process Design Kit(PDK)」と呼ばれる開発キットを購入

- <u>半導体ファウンドリ</u>が提供するPDKは<u>高価</u> → それが<u>無料 OSSに!</u>

- SkyWaterの130nmプロセス「SKY130」で半導体チップの製造を行うための設計を無料で行うことが可能

- GitHub google/skywater-pdk: Open source process design kit for usage with SkyWater Technology Foundry's 130nm node.

https://github.com/google/skywater-pdk

## Googleがカスタム半導体の民主化・自由化を推進

- · GoogleがスポンサとなりMPWシャトル・サービスを、無料で提供する

- FOSSi

- MPW(Multi-project wafer):

- さまざまな顧客からの異なる半導体チップを1枚のウェーハで製造する

- Skywater社で製造

- eFabless

- ・50万円~100万円出せば、作ってくれる道筋もある

- ・130nmプロセスのアナログ·デジタル混載LSIを作る。

### FOSSi(Free and Open Source Silicon Foundation)

- FOSSi(Free and Open Source Silicon Foundation)

- 無料のオープンデジタルハードウェア設計

- そのエコシステムを支援

- 非営利団体

- [FOSSi Dial-Up] Tim Ansell Skywater PDK: Fully open source manufacturable PDK for a 130nm process https://www.youtube.com/watch?v=EczW2IWdnOM

- 半導体チップの設計フロー3つの要素

- RTLデザイン ○

- EDAツール(電気、電子CAD) ○

- PDKデータ ← これがOSSに!

- 唯一オープンソース化がなされていなかったPDKデータがいよいよオープンソース化された

- FOSSIでは、半導体 試作を無料でできるサービスも提供

- (申込みが うまくできないが…)

- · GoogleがスポンサとなりMPWシャトル・サービスを、無料で提供する予定

- MPW(Multi-project wafer):

- さまざまな顧客からの異なる半導体チップを1枚のウェーハで製造する

- Skywater社で製造

### eFabless 事例1

• NEDO資金も受け、日本人 河崎氏も、

実際に、LSIを開発した。

※河崎氏は、RISC-V Foundation ボードメンバで、

JASA RISC-V WGメンバでもある

- 「Google社 が スポンサとなりeFabless社 の オープンソースシャトル を 使用し30日でRISC-V半導体 を 設計試作」

- https://riscv.or.jp/2022/05/marmot-risc-v-asic/

- JASA RISC-V WGとJASA OSS-WGは、頻繁に情報交換中

### eFabless 事例2

- 今村 謙之氏も、実際に、LSIを開発した。

- Kernel/VMレイヤーを自分色に染める! By ISHI会

https://www.slideshare.net/noritsuna/kernelvmby-ishi

イベント「はじめての半導体チップ設計」のアーカイブ動画を公開 https://ishi-kai.org/event/report/2023/08/25/AugustEvent \_0804\_Report.html

https://www.youtube.com/watch?v=W-HDNI4JK5A

#### FPGAでも非営利団体 OSFPGA Foundation

FPGAでも非営利団体 Open Source FPGA Foundation (OSFPGA Foundation) https://osfpga.org/

- 2021年4月8日、非営利団体「Open Source FPGA Foundation (OSFPGA Foundation)」の設立が発表された。

- OSFPGA Foundationは、オープンソースのFPGA設計ツールとIPブロックの普及推進を目的に組織された団体で、Open-Silicon社の創業者でSiFiveの会長も務めていた

- Naveed Sherwani氏が会長を務める。ボードメンバーには大学や研究機関の研究者が名を連ねており、FPGAベンダからはQuickLogicの社長兼CEOであるBrian Faith氏も参画している。同氏はオープンソースのチップ設計を目指す「CHIPS Alliance」やRISC-Vベースのオープンソースコアを

https://www.eda-express.com/2021/04/fpgaipopen-source-fpga-foundation.html

### 半導体チップの設計フロー3つの要素

- RTLデザイン 〇

- EDAツール 〇

- デジタル合成フロー〇

- PDKデータ ← これがOSSに

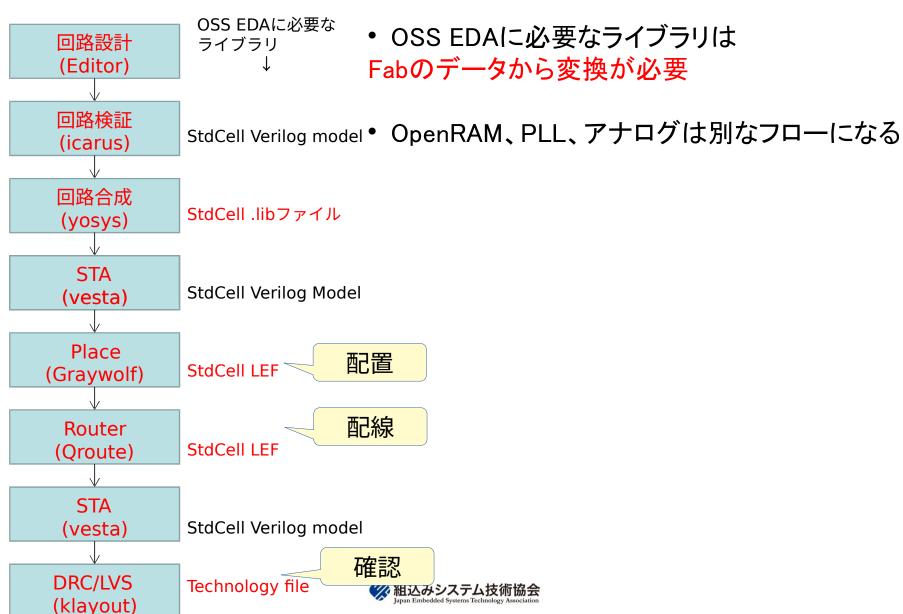

### OSSによるLSI開発のEDAフロー

ロジック部開発フロー

### デジタル合成フロー(Digital Synthesis Flow)

- Digital synthesis flowは、ツールと手法

- RTL → 物理回路 を合成

- FPGA ならば、Xilinx, Intel などのコンフィギュレーション・コード

- 特定の半導体工場(ファブ)で作るIC(LIS)の場合は、ファブのプロセス・ テクノロジでのレイアウト

- PDK情報が必要

- これまで

- 半導体用のデジタル合成フローは、

ケーデンスやシノプシス

という大手企業のみが供給していた

• FPGA 用は、Xilinx, Intel などFPGAメーカがツールを提供 OSSではないが、無料で配られていることも多い

# Graywolf OSSデジタル合成フロー・ツール

- トランジスタ配置ツール

- ・主にQflowと併用

- TimberWolf 6.3.5からフォークした

- TimberWolf はイェール大学で開発され、商用化されるまで、しばらくはオープンソースとして 配布された

- TimberWolf のオープンソース版の最後のバージョンは詳細ルーティングを実行しない

- しかし、プロ仕様の配置ツールだった

- graywolf の主な改善点

- ・ ビルド プロセスがより合理化された

- 通常の Linux ツールとして動作する

- 最初に環境変数を設定することなく

- どこからでも呼び出すことができる

https://github.com/rubund/graywolf

### Qflow OSSデジタル合成フロー・ツール

#### ※Graywolfと併用するのがよい

- デジタル合成フローは、verilog や VHDL などの高水準言語で書かれた回路 設計を物理回路に変換するために使用される一連のツールとメソッドです。

- Qflow 1.3: An Open-Source Digital Synthesis Flow

- http://opencircuitdesign.com/qflow/welcome.html

- OpenCores内 情報

- https://opencores.org/howto/eda

- Icarus Verilog Simulator: Verilog simulation and synthesis tool

- Verilator: free Verilog HDL simulator

- GHDL VHDL simulator

# OpenRAM: RAM合成ツール

- OpenRAMは、RAMを合成する

- 同時ではない、read/write のフツーのRAMは合 成できる

- OpenRAMは、同時1read & 1write のRAMが 仕様上は合成できるはず。

- だが、ダメ(残念)

### **Klayout**

- マスクの確認

- 分析

- https://www.klayout.de/

lacktriangle

```

# The PCell declaration for the circle

class StarPCell < PCellDeclarationHelper

include RBA

def initialize

# Important: initialize the super class

super

# declare the parameters

param(:1, TypeLayer, "Layer", :default = LayerInfo | new(1, 0))

param(:r1, TypeDouble, "Inner radius", :default = 1, :umit = "pu" param(:r2, TypeDouble, "Outer radius", :default = 5, :umit = "pu")

THE RESERVE OF THE PARTY OF THE

param(:n, TypeInt, "Number of rays", :default == 32)

param(:da, TypeInt, "Ray angle", :default == 5, :unit == "deg")

def display_text_impl

# Provide a descriptive text for the cell

"StarPCell(L=#{1,to s},R1=#{'%.3f' % r1.to f},R2=#{'%.3f' % r2.to

def produce impl

# This is the main part of the implementation: create the layou

# compute the ray parts and produce the polygons

d = Math::PI * da * 0.5 / 180.0

a = \theta.\theta

n.times do |i

DPoint::new(rl * Math.cos(a - d), rl * Math.sin(a - d))

DPoint::new(r1 * Math.cos(a + d), r1 * Math.sin(a + d)),

......

DPoint::new(r2 * Math.cos(a + d), r2 * Math.sin(a + d)),

DPoint::new(r2 * Math.cos(a - d), r2 * Math.sin(a - d))

cell.shapes(l_layer).insert(DPolygon.new(dpts))

a += Math::PI * 2 / n

end

```

# GAFAなどが自社向け半導体の開発 に力を入れる理由

- データセンタの消費電力 削減

- 自社製 専用半導体で電力削減

- 設計技術だけで自社半導体はできる

- 半導体工場レス

- RTL(デジタル論理)設計ができれば

- 専用アルゴリズム用LSI

- オーダーメイドICは、FPGAでは不満

- FPGAは消費電力 大

- FPGAは遅い

# 国内

- 政府が、LSI産業 再興

- JASAにも、経産省から LSI 開発者 教育についてヒアリングが来て、私もJASA技術本部長として応えました。

- LSI開発者の裾野を広げたい

- 産業技術総合研究所なども、OpenEDAに注目

# 国内

### 日本も、国の金で 施設を用意した

ふくおかIST(公益財団法人 福岡県産業・科学技術振興財団)

福岡システムLSI総合開発センター「システムLSI設計試作センター」

- http://www.ist.or.jp/lsi/pg04\_02.html

- ベンチャー企業が半導体の設計ツールを安価で利用できる

- LSI設計、少量 試作できる

- 50~100万円 あれば、LSIの少量生産ができる仕組みがある

#### 小規模EDA開発 日本でも流行

福岡システムLSI総合開発センター「システムLSI設計試作センター」の設計ツール一覧

| EDA###         |                        | 如ロタ                               |

|----------------|------------------------|-----------------------------------|

| EDA機能          |                        | 製品名                               |

| ハイレベル設計        | Cレベル合成                 | * CyberWorkBench ※NECの商品          |

| フロントエンド設計      | 論理シミュレータ               | * Incisive Enterprise Simulator L |

|                | 回路図エントリ                | * Schematic Editor                |

|                |                        | * ASCA                            |

|                |                        | * ASCA Basic                      |

|                | シミュレーションIF             | * Virtuoso ADE                    |

|                |                        | * ASCA Sim.faceA                  |

|                | 総合回路設計                 | • C <sup>3</sup>                  |

|                | Composer IFオプション       | * Composer IF                     |

|                | Verilog Interfaceオプション | * Verilog Interface               |

|                | SPICE Interfaceオプション   | * Analog HSPICE IF                |

|                | アナログ回路シミュレータ           | * Spectre circuit Sim             |

|                |                        | * Msim                            |

|                | 汎用回路波形解析               | * SimVision                       |

| レイアウト          | レイアウトエディタ              | * Virtuoso LE                     |

|                |                        | * ISMO                            |

|                | Cadence Linkオプション      | * Cadence Link (DF II Upgrade)    |

| レイアウト検証<br>その他 | DRC                    | * Calibre DRC                     |

|                | LVS                    | * Calibre LVS                     |

|                | IFオプション                | * Calibre RVE                     |

|                | DRC/ERC                | * iDRC/ERC                        |

|                | Caliber IFオプション        | * Calibre IF                      |

|                | 寄生パラメータ抽出              | * Calibre xRC                     |

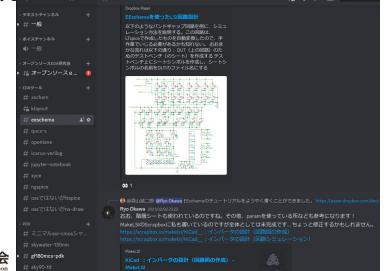

#### Open Source EDA Supporters (discode)

#### https://discord.com/channels/753405627564294176/93220997555883 2128

- OSS EDAをサポートする人たちの集まり

- 親切で優しい

- ふくおかIST のOSS EDAサーバのユーザ会

- サーバを維持するモチベーション

- オレオレ Open PDKを開発したり: 森山氏

- オレオレ Standard Cellライブラリを開発できるツールの開発

- オープンソースEDAフォーラム @福岡

- 2023/DEC/08

- JASA/OSSコンソーシアムも登壇予定

#### ミニマルファブ

#### 一般社団法人 ミニマルファブ推進機構

MINIMAL(Minimal Fab Promoting Organization)は、

半導体、MEMSなどマイクロデバイスの多品種少量生産を可能とする革新的な

産業システム(ミニマルファブ)の発展と普及を支援する世界唯一の団体です。

https://www.minimalfab.com/

- 半導体 1個を手作りで作れる

- 手間は掛かるが、費用は超安い

https://www.semiconportal.com/archive/editorial/conference/report/130705-minimalfab.html?printより引用

### 電子CAD OSS

## 電気/電子開発ツール

- いわゆるEDAツール(電気、電子CAD)

- Spice

- 電子回路シミュレータ

- KiCAD

- 回路図、基板CAD

### Spice

- 電子回路シミュレータ 無料版(必ずしもOSSではない)

- PSpice for TI

- PSpiceのTI強化版

https://www.tij.co.jp/tool/jp/PSPICE-FOR-TI

- LTspice

- アナログデバイセズ

https://www.analog.com/jp/design-center/design-tools-and-calc ulators/ltspice-simulator.html

https://www.ltspice.jp/information\_category/general/

Ngspice (OSS)

http://ngspice.sourceforge.net/

Qucs (OSS)

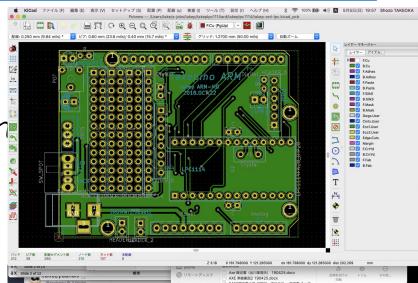

### **KiCAD**

- EDAツール(電気、電子CAD)

- https://www.kicad.org/

- KiCADがあれば、アマチュアでも基板が作れ

- 写真はたけおかが、KiCADで設計

- 中国でプリント基板少量生産

- シミュレーションはできない

- 知的な手助けは無い

- 高周波回路の引き回し補助とか無い

- Linux, Macでも動作

ArduinoフォームファクタのARM, MIPSマイコン

Raspi2,3用DCモータドライバ

### RISC-V

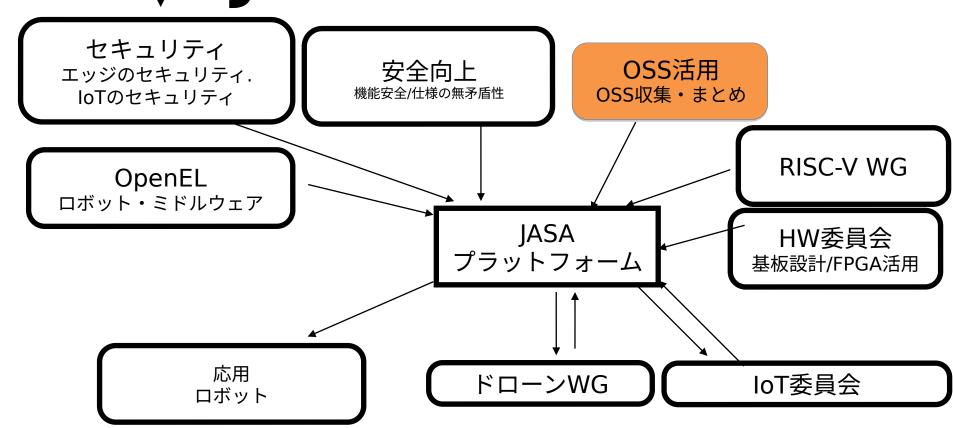

# JASA内の RISC-V関連 活動

# RISC-V

- ・命令セットの使用が無料

- ・自由に利用可能ないくつものCPUデザインがある

- ・BSDライセンス

- オープンかつ自由 または

- クローズドで独占的に

- ・派生成果物

- RISC-V自身と同様

- オープンかつ自由に、またはクローズドで独占的に、作成することを許可する。

TRASIO TEE

# JASA技術本部内

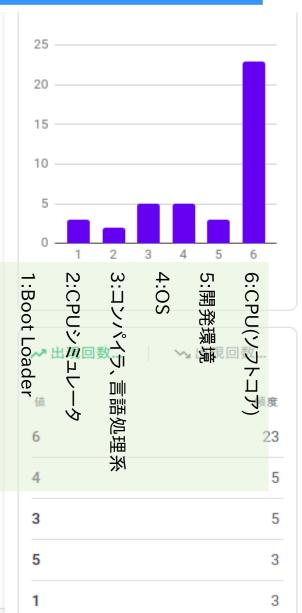

# OSS-WG RISC-V OSSコレクション

- RISC-V 用 OSS リスト

- OS, コンパイラ、開発環境

- RISC-V ソフトコア

- CPUコア論理

- 2020年春から、地道に情報更新

https://docs.google.com/spreadsheets/d/ 1nmeHG5HJanHjPiy3s145dYHLAiKgpcWrpNqpY\_2T bOU/edit?usp=sharing

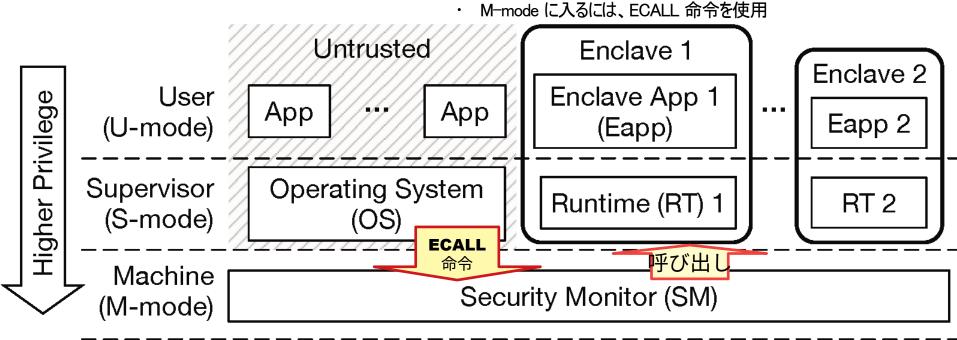

### TEE実装 Key stone が、どう動くか調査

http://docs.keystone-enclave.org/ オープンソース・プロジェクト ARMでいう Trust Zone と同等のものを、RISC-Vで実現

• OSSなので、ソースを読んで調査

- RISC-V(Key stoneが使用の実装)には、3つのレベルがある

- U-mode (User) / S-mode (Supervisor, OS) / M-mode (Trusted)

- M-modeのみ物理空間で、プロテクトできる(TrustWorld)

- U-mode や S-mode は仮想空間(通常のOSが使用)

Trusted Hardware

**RISC-V Cores**

Optional H/W Features

Root of Trust

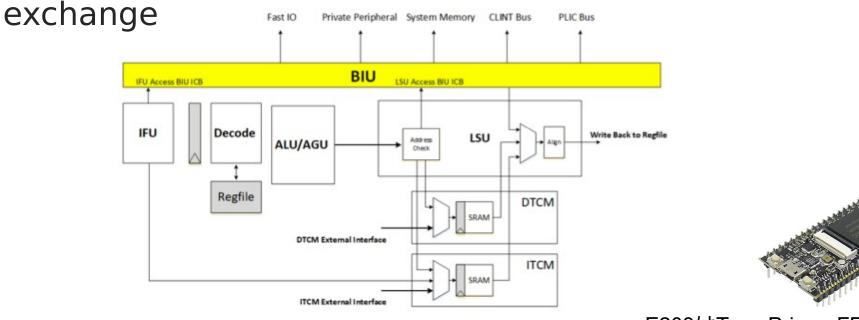

# Humming bird E203 core改造

- e203には、ビット操作拡張命令 "B"が入っていない

- ・オレオレ 命令 を追加

- population, parity, clz(count leading zero), ctz(count trailing zero)

- Float add, bit reverse, half word exchange, quarter word

図は下記より引用:

ITCM and DTCM is integrated inside Core

https://content.riscv.org/wp-content/uploads/2018/07/Shanghai-1110\_HummingBirdE200forShanghaiDay\_v1.pdf

E203はTang Primer FPGAボードで動作するRISC-Vソフトコア

# e203に命令追加した

変更したファイル

```

e203 defines.v : 全体のdefineたち

```

e203\_exu\_alu.v: alu計算のインプリメンテーション 実際の、計算はしない。write backなどを管理

e203 exu alu dpath.v: aluのデータ・パス。計算もする

e203 exu alu rglr.v : 一般alu命令のインプリメンテーション

e203 exu decode.v : 命令デコード

- ・オレオレ命令の実際の計算は、

- e203 exu alu dpath.v

- 命令デコードは、

- e203 exu decode.v

# AXEは東工大 吉瀬研RVCoreを改造中

吉瀬研 RVCore

https://www.arch.cs.titech.ac.jp/wk/rvcore/doku.php

- ・Gnu Prolog加速命令 追加(AXEとTELで特許 共同出願中)

- ハードウェア・マルチスレッド機構 追加

- 時分割マルチスレッド

- ハードウェアのセマフォ機構

- 外部イベント→セマフォ結びつけ

- LL/SCによる排他制御機構

- OS機能を、ハードウェア化 → 省メモリ、省電力化

### SPARCもオープンソースなソフトコアあり

Open Sparc

https://www.oracle.com/servers/technologies/opensparc-overview.html

- LEONシリーズ

- ・欧州宇宙機関(ESA)が積極開発

- Open Sparc の継続

https://en.wikipedia.org/wiki/LEON

- Len3, 3FT,4,5

- LEON3FT : Fault-tolerant processor

```

https://www.gaisler.com/index.php/products/ipcores

https://www.gaisler.com/index.php/products/

processors/leon3

```

- Leon3 はGPL

- SPARC v8 が FPGAでも動作

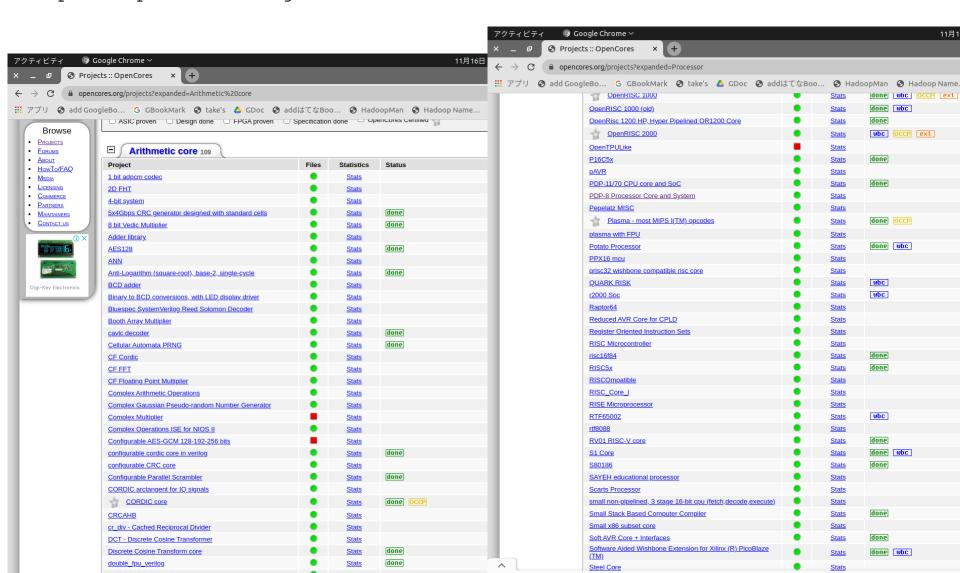

### オープンソースなソフトコア

#### Opencores

https://opencores.org/

#### OSS-WG OSSハンズオン

テーマ: エッジデバイスプロトタイピングで深めるOSS活用WG

概要: 従来の座学のみで完結する勉強会ではなく、エッジデバイスを用いたハンズオンを中心としたチーム 単位でのプロト開発を通じてOSS活用技術の向上を目指します

**実施方式**: 各自のやってみたいコトを共通項に企業の枠を超えたチームを編成し、エッジデバイスを利用しながらチームで定めたテーマに基づきワークショップ形式(全5回程度)で実施

#### 実績:

- 2023年度 全4回開催+報告会の予定で、実施中

- 2022年度 全4回開催+報告会実施。参加者9名、3チーム編成

- 2021年度 全4回開催+報告会実施。参加者9名、3チーム編成

- 2020年度 全4回開催+報告会実施。参加者14名(内7社、男性:13名、女性:1名)、4チーム編成

- 2019年度 全4回開催+報告会を実施。参加者8名(内4社、男性:6名、女性:2名)、3チーム編成

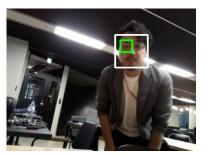

ワーキングの様子。 企業間でチームを編成し、 ハンズオンに取り組む

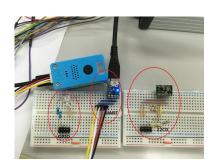

2021年度は液晶+WiFi マイコンのM5 Stickを使ったハンズオンでAlあり、IoTありとバラエティがあった

報告会のデモ。ラズパイとカ メラと人感センサーで作成し た社内来客検知で顔検出を 行ったところ

2020年度はAIマイコンの M5SticVを使ったハンズオンで エッジAIにも取り組んでいる

### FPGAハンズオン(OSSコンソーシアムAIR部会と共同開催)

- FPGA開発入門ハンズオンを開催

- 2023/MAR/17 午後

- 於 秋葉原 「ふれあい貸し会議室 秋葉原No51」

- 受講者4名

- 対象FPGA: Anlogic Technologies EG4S20

- Sipeed TANG PriMER FPGA開発ボード

- ・オリジナル基板は、OSSコンソーシアム有志が開発

- 費用も、OSSコンソーシアムが出した

- ・好評であった

- ・論理回路設計,LSI設計開発者を増やしたい

#### 「OSSによるLSI開発OpenEDAとRISC-V(update)」

2023/11/15 発行

発行者 一般社団法人 組込みシステム技術協会 東京都 中央区 入船 1-5-11 TEL: 03(6372)0211 FAX: 03(6372)0212 URL:http://www.jasa.or.jp/

本書の著作権は一般社団法人組込みシステム技術協会(以下、JASA)が有します。

JASAの許可無く、本書の複製、再配布、譲渡、展示はできません。 また本書の改変、翻案、翻訳の権利はJASAが占有します。 その他、JASAが定めた著作権規程に準じます。